)领域,需要处理的数据量很大,并且实时性要求很高。传统的DSP设计方法主要有采用固定功能的DSP器件和采用DSP在执行时的顺序性,限制了它们在高速和实时系统中的应用。随着深亚微米半导体制造工艺的不断创新,百万门可

然而在应用FPGA进行系统设计综合过程中,选择芯片的运行速度优化和资源利用优化常常是相互矛盾的,对速度指标要求高的设计优化常常要占用较大的芯片资源,而减小芯片面积的设计又需要以降低系统速度为代价。从FPGA发展趋势和DSP运算要求看,系统速度指标的意义比面积指标更趋重要,需要我们进一步深入研究提高芯片的最高工作速度的设计策略。我们需要讨论一下基于FPGA的DSP系统设计中的流水线技术主要应用在哪些方面?

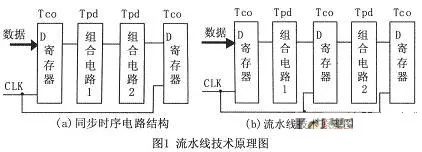

流水线是一种在时间上串行,在空间上并行的技术,其基本原理如图1所示。将整个电路划分为若干个流水线级,流水线每级之间设置寄存器锁存上一级输出的数据;每一级只完成数据处理的一部分;一个时钟周期完成一级数据处理,然后在下一个时钟到来时将处理后的数据传递给下一级;第一组数据进入流水线后,经过一个时钟周期传到第二级,同时第二组数据进入第一级,数据队列依次前进。每组数据都要经过所有的流水级后才能得到最后的计算结果,但是对整个流水线而言,每个时钟都能计算出一组结果,所以平均计算一组数据只需要一个时钟周期的时间,这样就大大提高了数据处理速度,电路在单位时间内处理的数据量就愈大,即电路的吞吐量就越大,保证整个系统以较高的频率工作。

FPGA的结构特点很适合采用流水线设计,以Altera低成本系列Cyclone II为例,不仅有最多达68416个逻辑单元(LE),而且提供嵌入式存储资源支持各种存储应用和低成本DSP应用(如乘法器模块、PLL)。每个LE均含有一个四输入查找表LUT、一个可编程触发器等。一般设计中,这个触发器或者没有用到,或者用来存储布线资源。设计中可将一个算术操作分解成一些小规模的基本操作配置到LUT中,将进位和中间值存储在寄存器中,在下一个时钟内继续运算。因此,在FPGA中采用流水线技术,只需要极少或者根本不需要额外的资源成本。特别是在需要进行大批量重复运算的场合,如数字信号处理中的卷积操作、FFT或FIR滤波器设计,采用流水线技术,可以大大提高系统运行速度。

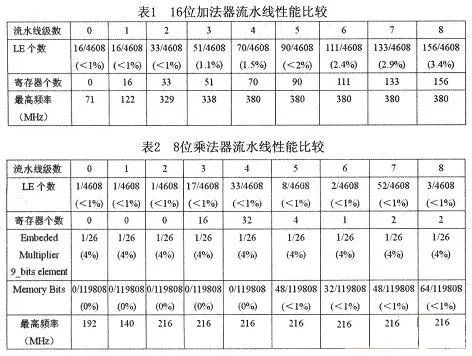

加法器和乘法器是DSP中最基本的运算部件。在Quartus软件平台上设计加法器或乘法器可以采用原理图法和VHDL语言两种基本方法。考虑到参数可设置宏模块(Library of Parameterrized Modtlles-LPM)经过严格测试和优化,可以发挥最佳性能,所以,我们采用原理图设计方式,通过MegaWizard P1ug-In Manager工具引入1pmadsub和1pm mult两种可设置流水线的LPM模块,实现了不同位宽、不同流水线级数的加法器和乘法器设计,并选用CycloneII系列EP2C5Q208C7器件进行了综合、布局布线、时序分析和仿真设计,以比较其性能的变化特征。

(1)采用流水线技术普遍比不用流水线工作速度显著提高,体现流水线技术在高速DSP运算上的优势。

(3)采用不同的流水线级数在速度指标和资源耗用率上有所不同,流水线级数增加,速度指标不一定增加,但资源耗用大大增加,所以应注意速度和资源耗用指标的权衡。如对16位加法器,如不用M4K(专用存储器资源),以采用2级流水线级流水最佳。对于其他DSP运算,在设计时必须通过反复比较、设计,选择符合系统性能要求的流水线 不同位宽运算器相同流水线级数的性能比较

对采用6级流水的加法器和乘法器的数据位宽加以改变,通过综合仿真,分析其性能指标的变化,见表3。

由比较结果可见:采用同样的流水线级数时,工作速度基本相同,但耗用资源随输入位数的增加而急剧增加,加法器主要是逻辑单元LE个数的增加;乘法器则是存储器位和嵌入式乘法器个数的增加。因此,对于不同的运算器电路,应根据需要选用不同型号的FPGA器件以满足对不同资源的需要。如,仅作加法运算时,可以选用逻辑单元丰富的FPGA器件女HACEX系列、FLEX等系列;乘加运算则需要选择内嵌乘法器模块和存储器模块的Cyclone、CycloneII等系列。

PELINE的LPM模块,并利用QuartusII(提供了40多种LPM函数)编译器给出的LPM PIPELINE最佳数值(即最佳流水线级数),设定最佳LPM_PIPEINE值。在无合适的I PM模块可用时,需要用VHDL作为设计输入。

流水线技术的实质就是在适当的地方加入寄存器,将前面的运算结果或输入数据暂存,并在下一个时钟到来时,将寄存值作为后一级运算的输入。因此在用VHDL描述流水线时,只需对不含流水线的运算器描述代码作适当改写,施加必要的设计约束即可实现。一般通过在进程中加入W

T语句或IF_THEN语句来测试敏感信号边沿,实现寄存器或锁存器。如使用WAIT语句,常用的描述形式为:

另外,用VHDL设计输入时也可以利用Altera所提供的LPM函数,但必须在设计实体前使LPM库可现,即加入以下语句:

对图1所示系统进行延时分析,图中组合逻辑的延迟包括两级,合理设计的流水线结构中,其延迟时间应大致相等,设为2Tpd,插入每级寄存器组的触发时间为Tco。因此,从输入到输出总的等待时延为:TDl=2(Tpd+Tco),称为流水线设计的首次延时(Fi

t Latency)。对于连续的运算,由于加上寄存器组后,每级计算后的中间结果都能暂时保存,下一个时钟到来时,可以直接参与下一级逻辑运算,无需等待从系统的输入端传来数据。因此,第二个结果及以后的运算结果的获得只需要一个时钟周期,等待的时延为:TD2=Tpd+TCO。可见,流水线设计的首次延时与流水线正常延时相比要长得多。所以在选择是否采用流水线技术时,要分析DSP运算的频率。当需要进行连续运算(即流水线一直是满负荷)时,采用流水线可以大大提高数据吞吐率;但如果只是偶尔需要加、乘运算,由于首次延时大于非流水线方式下的pin to pin延时,流水线应用效果变差,而且还牺牲了额外的芯片资源,所以不

使用流水线。在FPGA/CPLD中,器件的延时Tpd要比寄存器的触发时间TCO长得多,一般分析流水线吞吐延时可以忽略TCO。但是在高速运算场合或流水线技术较多时(如视频信号处理或无线通信中的数据处理),TCO与Tpd相比已不可忽略,必须仔细选择流水线的级数,防止TCO的影响造成流水线 嵌入式存储器块资源的充分利用在FPGA器件中,嵌入式存储器块(Embedded Mem

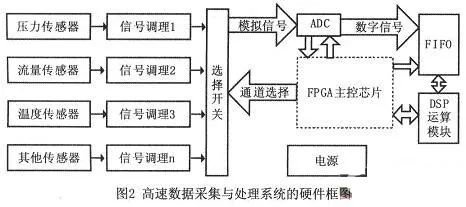

FLEX10K系列器件提供了3个嵌入式阵列块EAB,每个EAB提供可灵活设置的2048位RAM,Cyclone系列提供了数十个M4K资源,每个M4K提供4608位RAM,可单独使用,也可组合使用。使用EAB或M4K构建运算器如乘法器,实质是构成乘法查找表,其运算速度比采用LPM的乘法器速度更快,只是由于资源有限,只能实现小型乘法器。如能把基于嵌入式阵列块的小型乘法器和流水线技术相结合,则能够实现运算量和速度的进一步提高。2.4 控制流水线和数据流水线的划分由于数字信号处理系统复杂性的不断提高,在利用流水线技术实现DSP运算设计时,还有一个需要考虑的问题就是控制流水线和数据流水线的划分问题。如在高速数据采集与处理系统中,采样数据的处理主要涉及DSP运算,可以归入数据流水线。各输入通道

与信号调理电路的选通控制、模数转换、数据缓冲与传送、数据运算控制则需要主控芯片完成,如图2所示。高速主控芯片可以选用FPGA器件,采用流水线技术,将数据采集与处理过程中的通道选择、模数转换、数据缓冲与发送、数据运算四部分的控制过程设计为四级流水线进程,以减少数据采集与处理的平均作业时间,实现高速率的数据采集。主控芯片的流水线技术可以归入控制流水线 结论

通过实验对比,验证了利用流水线技术可以实现基于FPGA器件的高速DSP运算。在具体运算器设计中要通过综合过程,比较和优选流水线级数以满足速度和资源优化的需要。DSP系统在进行流水线设计时要根据运算频率明确用否流水线,合理划分控制流水线和数据流水线,还要注意合理选用原理图和VHDL描述,充分利用带有LPM_PIPELINE的LPM和EAB(M4K)等资源,最大限度提高系统数据吞吐率和设计效率。

速度指标的意义比面积指标更趋重要,需要我们进一步深入研究提高芯片的最高工作速度的设计策略。我们需要讨论一下基于

,cina_reg[3:0]} + {1b0,cinb_reg[3:0]} + cout1 ,sum1[3:0]} ;endendmodule这里讲到的

的并行高效FIR滤波器设计 /

的平面设计应当保证零件的运输路线最短,生产工人操作方便,辅助服务部门工作便利,最有效地利用生产面积,并考虑

又称为装配线,一种工业上的生产方式,指每一个生产单位只专注处理某一个片段的工作。以提高工作效率及产量;按照